Novel system architecture results in 33.9% increase in computer system performance

It is predicted that by 2018 computers will be capable of a billion billion calculations per second. That means they will require 1000 times more memory than is available today. One essential type of memory, DRAM, is reaching its performance limit for energy efficiency and transistor scaling.

It is predicted that by 2018 computers will be capable of a billion billion calculations per second. That means they will require 1000 times more memory than is available today. One essential type of memory, DRAM, is reaching its performance limit for energy efficiency and transistor scaling.

Phase Change Memory (PCM) is a leading contender to replace DRAM. It outperforms in both power usage and scalability and, unlike DRAM, PCM stores data permanently instead of losing it if the power goes out. This is similar to other permanent memory devices, like the familiar flash drive, but PCM is more reliable and over 100 times faster than flash.

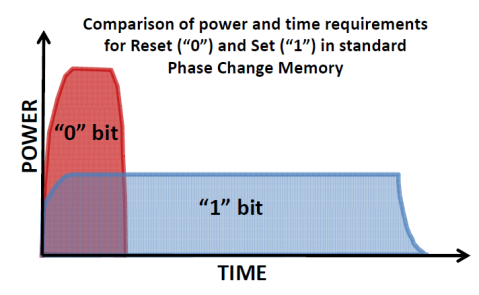

However, PCM has a major weakness: slow data write speed. This is due to characteristics of the chip material that cause writing a “1” data bit to be slower than writing a “0” bit. So the speed of writing a bit sequence is always limited by the ones present. The chip also requires more electrical current to write a zero than a one. As a result, the zeros present limit the number of PCM cells that can be written concurrently.

Researchers at UMaine have developed a unique device architecture that groups ones and zeros together in separate bundles to be written in the order that best optimizes write speed and also saves memory so it may be used for other operations. Writing all of the zeros together eliminates the fast-slow disparity that occurs between ones and zeros written in mixed sequence. And writing all of the low-energy ones together allows more memory cells to be written in parallel under the same power constraints. This provides an overall system improvement of 33.9% compared to standard PCM.